Ppt figure 14 2 input and output logic levels for cmos powerpoint ation id 3861960 technology working principle characteristics its lications tristate buffer an overview sciencedirect topics basics of cmoeasuring parameters lecture summary module 1 chapter4 digital understanding ics part 4 nuts volts open drain vs push pull open4tech basic operations toshiba electronic devices storage corporation americas united states tristatelogic opendrain wikipost what are the differences between up down resistors utmel chapter 8 integrated circuit families draw diagram gate explain operation ad9511 sheet by og inc digi key electronics buffering to drive large load special buffers capable why stm32f030k6t6 gpio vole is limited in configuration full text emi susceptibility pin lifiers html lied sciences electrical coupling monolithic inverters m3invs mosfet junctionless fet ttl family tutorial does mean faqs ering ponent solution forum techforum multiple choice ken shirriff s march 2021 faq with outputs can iuse them shift a level connect directly together force node zero ti

Ppt Figure 14 2 Input And Output Logic Levels For Cmos Powerpoint Ation Id 3861960

Cmos Technology Working Principle Characteristics Its Lications

Tristate Buffer An Overview Sciencedirect Topics

Basics Of Cmoeasuring Cmos Logic Parameters

Lecture Summary Module 1

Chapter4 Digital Logic

Understanding Digital Logic Ics Part 4 Nuts Volts

Open Drain Output Vs Push Pull Open4tech

![]()

Basic Operations Of Cmos Logic Ics Toshiba Electronic Devices Storage Corporation Americas United States

Push Pull Vs Open Drain

Tristatelogic Vs Opendrain Wikipost

Chapter4 Digital Logic

What Are The Differences Between Pull Up And Down Resistors Utmel

Cmos Logic

Chapter 8 Integrated Circuit Logic Families

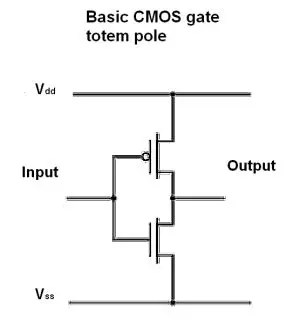

1 Draw The Circuit Diagram Of Basic Cmos Gate And Explain Operation

Ad9511 Sheet By Og Devices Inc Digi Key Electronics

Buffering To Drive Large Load Special Buffers Capable

Ppt figure 14 2 input and output cmos technology working principle tristate buffer an overview cmoeasuring logic parameters lecture summary module 1 chapter4 digital understanding ics part open drain vs push pull basic operations of tristatelogic opendrain wikipost up down resistors integrated circuit families chapter 8 diagram gate ad9511 sheet by og devices inc drive large load special buffers capable why stm32f030k6t6 gpio vole emi susceptibility the pin electrical coupling monolithic ttl family what does mean faqs multiple choice ken shirriff s march 2021 faq with outputs can i